# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## Preliminary

Notice: This is not final specification. Some parametric limits are subject to change.

### **DESCRIPTION**

The M5M5V5636GP is a family of 18M bit synchronous SRAMs organized as 524288-words by 36-bit. It is designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Mitsubishi's SRAMs are fabricated with high performance, low power CMOS technology, providing greater reliability. M5M5V5636GP operates on 3.3V power/ 2.5V I/O supply or a single 3.3V power supply and are 3.3V CMOS compatible.

### **FEATURES**

- Fully registered inputs and outputs for pipelined operation

- Fast clock speed: 250, 225, and 200MHz

- Fast access time: 2.6, 2.8 ns and 3.2ns

- Single 3.3V -5% and +5% power supply VDD

- Separate VDDQ for 3.3V or 2.5V I/O

- Individual byte write (BWa# BWd#) controls may be tied

I OW

- Single Read/Write control pin (W#)

- CKE# pin to enable clock and suspend operations

- Internally self-timed, registers outputs eliminate the need to control G#

- Snooze mode (ZZ) for power down

- Linear or Interleaved Burst Modes

- Three chip enables for simple depth expansion

#### **Package**

100pin TQFP

#### **APPLICATION**

High-end networking products that require high bandwidth, such as switches and routers.

### **FUNCTION**

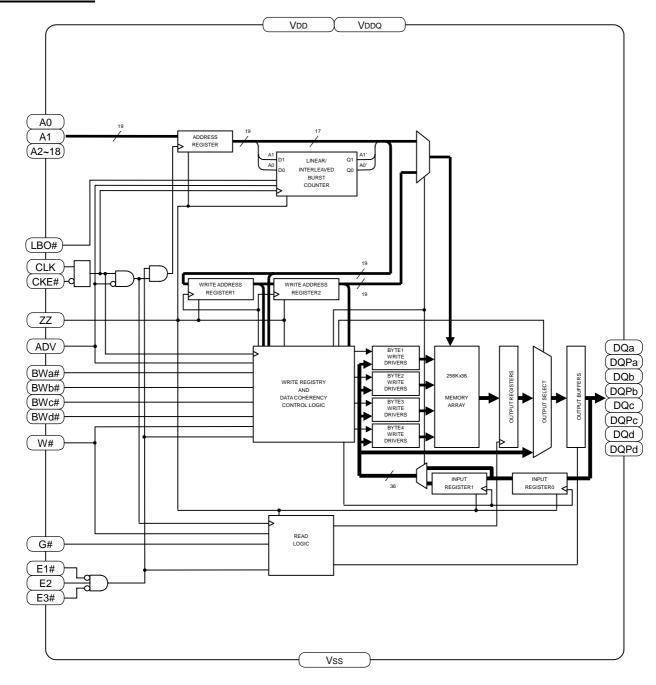

Synchronous circuitry allows for precise cycle control triggered by a positive edge clock transition.

Synchronous signals include: all Addresses, all Data Inputs, all Chip Enables (E1#, E2, E3#), Address Advance/Load (ADV), Clock Enable (CKE#), Byte Write Enables (BWa#, BWb#, BWc#, BWd#) and Read/Write (W#). Write operations are controlled by the four Byte Write Enables (BWa# - BWd#) and Read/Write(W#) inputs. All writes are conducted with on-chip synchronous self-timed write circuitry.

Asynchronous inputs include Output Enable (G#), Clock (CLK) and Snooze Enable (ZZ). The HIGH input of ZZ pin puts the SRAM in the power-down state. The Linear Burst order (LBO#) is DC operated pin. LBO# pin will allow the choice of either an interleaved burst, or a linear burst.

All read, write and deselect cycles are initiated by the ADV LOW input. Subsequent burst address can be internally generated as controlled by the ADV HIGH input.

### **PART NAME TABLE**

| Part Name        | Frequency | Access | Cycle | Active Current (max.) | Standby Current (max.) |

|------------------|-----------|--------|-------|-----------------------|------------------------|

| M5M5V5636GP - 25 | 250MHz    | 2.6ns  | 4.0ns | 550mA                 | 30mA                   |

| M5M5V5636GP - 22 | 225MHz    | 2.8ns  | 4.4ns | 500mA                 | 30mA                   |

| M5M5V5636GP - 20 | 200MHz    | 3.2ns  | 5.0ns | 440mA                 | 30mA                   |

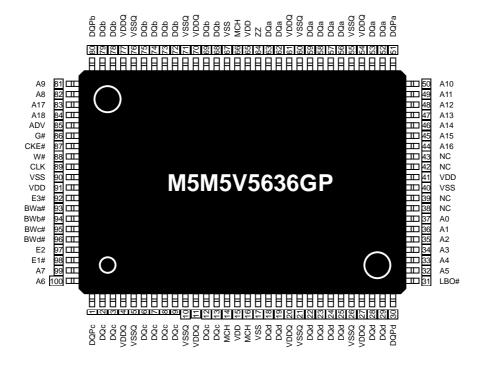

### PIN CONFIGURATION(TOP VIEW)

### 100pin TQFP

Note1. MCH means "Must Connect High". MCH should be connected to HIGH.

### **BLOCK DIAGRAM**

Note3. The BLOCK DIAGRAM illustrates simplified device operation. See TRUTH TABLE, PIN FUNCTION and timing diagrams for detailed information.

## M5M5V5636GP -25,22,20 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **PIN FUNCTION**

| Pin                                    | Name                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0~A18                                 | Synchronous<br>Address<br>Inputs       | These inputs are registered and must meet the setup and hold times around the rising edge of CLK. A0 and A1 are the two least significant bits (LSB) of the address field and set the internal burst counter if burst is desired.                                                                                                                                                                                         |

| BWa#, BWb#,<br>BWc#, BWd#              | Synchronous<br>Byte Write<br>Enables   | These active LOW inputs allow individual bytes to be written when a WRITE cycle is active and must meet the setup and hold times around the rising edge of CLK. BYTE WRITEs need to be asserted on the same cycle as the address. BWs are associated with addresses and apply to subsequent data. BWa# controls DQa, DQPa pins; BWb# controls DQb, DQPb pins; BWc# controls DQc, DQPc pins; BWd# controls DQd, DQPd pins. |

| CLK                                    | Clock Input                            | This signal registers the address, data, chip enables, byte write enables and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                                                                                              |

| E1#                                    | Synchronous<br>Chip Enable             | This active LOW input is used to enable the device and is sampled only when a new external address is loaded (ADV is LOW).                                                                                                                                                                                                                                                                                                |

| E2                                     | Synchronous<br>Chip Enable             | This active High input is used to enable the device and is sampled only when a new external address is loaded (ADV is LOW). This input can be used for memory depth expansion.                                                                                                                                                                                                                                            |

| E3#                                    | Synchronous<br>Chip Enable             | This active Low input is used to enable the device and is sampled only when a new external address is loaded (ADV is LOW). This input can be used for memory depth expansion.                                                                                                                                                                                                                                             |

| G#                                     | Output Enable                          | This active LOW asynchronous input enable the data I/O output drivers.                                                                                                                                                                                                                                                                                                                                                    |

| ADV                                    | Synchronous<br>Address<br>Advance/Load | When HIGH, this input is used to advance the internal burst counter, controlling burst access after the external address is loaded. When HIGH, W# is ignored. A LOW on this pin permits a new address to be loaded at CLK rising edge.                                                                                                                                                                                    |

| CKE#                                   | Synchronous<br>Clock Enable            | This active LOW input permits CLK to propagate throughout the device. When HIGH, the device ignores the CLK input and effectively internally extends the previous CLK cycle. This input must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                     |

| ZZ                                     | Snooze<br>Enable                       | This active HIGH asynchronous input causes the device to enter a low-power standby mode in which all data in the memory array is retained. When active, all other inputs are ignored. When this pin is LOW or NC, the SRAM normally operates.                                                                                                                                                                             |

| W#                                     | Synchronous<br>Read/Write              | This active input determines the cycle type when ADV is LOW. This is the only means for determining READs and WRITEs. READ cycles may not be converted into WRITEs (and vice versa) other than by loading a new address. A LOW on the pin permits BYTE WRITE operations and must meet the setup and hold times around the rising edge of CLK. Full bus width WRITEs occur if all byte write enables are LOW.              |

| DQa,DQPa,DQb,DQPb<br>DQc,DQPc,DQd,DQPd | Synchronous<br>Data I/O                | Byte "a" is DQa, DQPa pins; Byte "b" is DQb, DQPb pins; Byte "c" is DQc, DQPc pins; Byte "d" is DQd,DQPd pins. Input data must meet setup and hold times around CLK rising edge.                                                                                                                                                                                                                                          |

| LBO#                                   | Burst Mode<br>Control                  | This DC operated pin allows the choice of either an interleaved burst or a linear burst. If this pin is HIGH or NC, an interleaved burst occurs. When this pin is LOW, a linear burst occurs, and input leak current to this pin.                                                                                                                                                                                         |

| VDD                                    | VDD                                    | Core Power Supply                                                                                                                                                                                                                                                                                                                                                                                                         |

| Vss                                    | Vss                                    | Core Ground                                                                                                                                                                                                                                                                                                                                                                                                               |

| VDDQ                                   | VDDQ                                   | I/O buffer Power supply                                                                                                                                                                                                                                                                                                                                                                                                   |

| Vssq                                   | Vssq                                   | I/O buffer Ground                                                                                                                                                                                                                                                                                                                                                                                                         |

| MCH                                    | Must Connect High                      | These pins should be connected to HIGH                                                                                                                                                                                                                                                                                                                                                                                    |

| NC                                     | No Connect                             | These pins are not internally connected and may be connected to ground.                                                                                                                                                                                                                                                                                                                                                   |

### **DC OPERATED TRUTH TABLE**

| Name | Input Status | Operation                  |

|------|--------------|----------------------------|

| LBO# | HIGH or NC   | Interleaved Burst Sequence |

| LBO# | LOW          | Linear Burst Sequence      |

Note4. LBO# is DC operated pin.

Note5. NC means No Connection.

Note6. See BURST SEQUENCE TABLE about interleaved and Linear Burst Sequence.

### **BURST SEQUENCE TABLE**

Interleaved Burst Sequence (when LBO# = HIGH or NC)

| Operation                            | A18~A2         | A1,A0 |       |       |     |  |  |

|--------------------------------------|----------------|-------|-------|-------|-----|--|--|

| First access, latch external address | A18~A2         | 0,0   | 0 , 1 | 1,0   | 1,1 |  |  |

| Second access(first burst address)   | latched A18~A2 | 0,1   | 0,0   | 1 , 1 | 1,0 |  |  |

| Third access(second burst address)   | latched A18~A2 | 1,0   | 1,1   | 0,0   | 0,1 |  |  |

| Fourth access(third burst address)   | latched A18~A2 | 1,1   | 1,0   | 0,1   | 0,0 |  |  |

### **Linear Burst Sequence** (when LBO# = LOW)

| Operation                            | A18~A2         | A1,A0 |       |       |       |  |  |

|--------------------------------------|----------------|-------|-------|-------|-------|--|--|

| First access, latch external address | A18~A2         | 0,0   | 0 , 1 | 1,0   | 1,1   |  |  |

| Second access(first burst address)   | latched A18~A2 | 0 , 1 | 1,0   | 1 , 1 | 0,0   |  |  |

| Third access(second burst address)   | latched A18~A2 | 1,0   | 1 , 1 | 0,0   | 0 , 1 |  |  |

| Fourth access(third burst address)   | latched A18~A2 | 1 , 1 | 0,0   | 0 , 1 | 1,0   |  |  |

Note7. The burst sequence wraps around to its initial state upon completion.

### **TRUTH TABLE**

| E1# | E2 | E3# | ZZ | ADV | W# | BWx# | G# | CKE# | CLK  | DQ     | Address<br>used | Operation                    |

|-----|----|-----|----|-----|----|------|----|------|------|--------|-----------------|------------------------------|

| Н   | Χ  | Χ   | L  | L   | Χ  | Х    | Χ  | L    | L->H | High-Z | None            | Deselect Cycle               |

| Χ   | L  | Х   | L  | L   | Χ  | Х    | Χ  | L    | L->H | High-Z | None            | Deselect Cycle               |

| Χ   | Χ  | Н   | L  | L   | Χ  | X    | Χ  | L    | L->H | High-Z | None            | Deselect Cycle               |

| Χ   | Χ  | Х   | L  | Н   | Χ  | Х    | Χ  | L    | L->H | High-Z | None            | Continue Deselect Cycle      |

| L   | Н  | L   | L  | L   | Н  | Х    | L  | L    | L->H | Q      | External        | Read Cycle, Begin Burst      |

| Χ   | Χ  | Х   | L  | Н   | Χ  | Х    | L  | L    | L->H | Q      | Next            | Read Cycle, Continue Burst   |

| L   | Н  | L   | L  | L   | Н  | Х    | Н  | L    | L->H | High-Z | External        | NOP/Dummy Read, Begin Burst  |

| Χ   | Χ  | Х   | L  | Н   | Χ  | Х    | Н  | L    | L->H | High-Z | Next            | Dummy Read, Continue Burst   |

| ┙   | Η  | L   | Ш  | L   | ٦  | L    | Χ  | L    | L->H | D      | External        | Write Cycle, Begin Burst     |

| Χ   | Χ  | Х   | L  | Н   | Χ  | L    | Χ  | L    | L->H | D      | Next            | Write Cycle, Continue Burst  |

| L   | Н  | L   | L  | L   | L  | Н    | X  | L    | L->H | High-Z | None            | NOP/Write Abort, Begin Burst |

| Χ   | Χ  | Χ   | L  | Н   | Χ  | Н    | Χ  | L    | L->H | High-Z | Next            | Write Abort, Continue Burst  |

| Χ   | Χ  | X   | L  | Х   | Χ  | Χ    | Χ  | Н    | L->H | 1      | Current         | Ignore Clock edge, Stall     |

| X   | Χ  | X   | Н  | X   | Χ  | X    | Χ  | Χ    | Χ    | High-Z | None            | Snooze Mode                  |

Note8. "H" = input VIH; "L" = input VIL; "X" = input VIH or VIL.

Note9. BWx#=H means all Synchronous Byte Write Enables (BWa#,BWb#,BWc#,BWd#) are HIGH. BWx#=L means one or more Synchronous Byte Write Enables are LOW.

Note10. All inputs except G# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

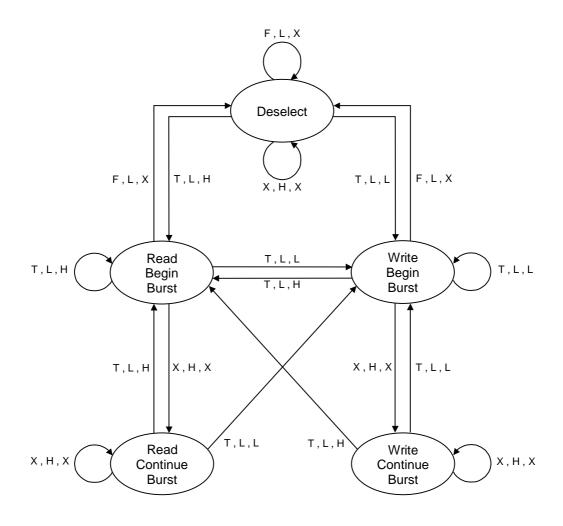

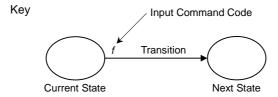

### **STATE DIAGRAM**

Note11. The notation "x , x , x" controlling the state transitions above indicate the state of inputs E, ADV and W# respectively.

Note12. If (E1# = L and E2 = H and E3# = L) then E="T" else E="F". Note13. "H" = input VIH; "L" = input VIL; "X" = input VIH or VIL; "T" = input "false".

### **WRITE TRUTH TABLE**

| W# | BWa# | BWb# | BWc# | BWd# | Function        |

|----|------|------|------|------|-----------------|

| Н  | Х    | Х    | Х    | Х    | Read            |

| L  | L    | Н    | Н    | Н    | Write Byte a    |

| L  | Н    | L    | Н    | Н    | Write Byte b    |

| L  | Н    | Н    | L    | Н    | Write Byte c    |

| L  | Н    | Н    | Н    | L    | Write Byte d    |

| L  | L    | L    | L    | L    | Write All Bytes |

| L  | Н    | Н    | Н    | Н    | Write Abort/NOP |

Note14. "H" = input VIH; "L" = input VIL; "X" = input VIH or VIL.

Note15. All inputs except G# and ZZ must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol     | Parameter                       | Conditions          | Ratings         | Unit |

|------------|---------------------------------|---------------------|-----------------|------|

| Vdd        | Power Supply Voltage            |                     | -1.0*~4.6       | V    |

| VDDQ       | I/O Buffer Power Supply Voltage | With respect to Voc | -1.0*~4.6       | V    |

| VI         | Input Voltage                   | With respect to Vss | -1.0~VDDQ+1.0** | V    |

| Vo         | Output Voltage                  |                     | -1.0~VDDQ+1.0** | V    |

| PD         | Maximum Power Dissipation (VDD) |                     | 1180            | mW   |

| TOPR       | Operating Temperature           |                     | 0~70            | °C   |

| TSTG(bias) | Storage Temperature(bias)       |                     | -10~85          | °C   |

| Tstg       | Storage Temperature             |                     | -65~150         | °C   |

Note16.\* This is –1.0V when pulse width≤2ns, and –0.5V in case of DC.

<sup>\*\*</sup> This is -1.0V~VDDQ+1.0V when pulse width≤2ns, and -0.5V~VDDQ+0.5V in case of DC.

### DC ELECTRICAL CHARACTERISTICS (Ta=0~70°C, VDD=3.135~3.465V, unless otherwise noted)

| Cumahal | Deservator                                      | 0-                                                          | ndition                     | Lir      | nits         | Unit |

|---------|-------------------------------------------------|-------------------------------------------------------------|-----------------------------|----------|--------------|------|

| Symbol  | Parameter                                       |                                                             | naition                     | Min      | Max          | Unit |

| Vdd     | Power Supply Voltage                            |                                                             |                             | 3.135    | 3.465        | V    |

| \/==0   | 1/0 D " D 0 1 1 1/1 1/1                         | VDDQ = 3.3V                                                 |                             | 3.135    | 3.465        | .,   |

| VDDQ    | I/O Buffer Power Supply Voltage                 | VDDQ = 2.5V                                                 | VDDQ = 2.5V                 |          | 2.625        | V    |

| \ /     | LP ale laval lava (Malia aa                     | VDDQ = 3.135~3.46                                           | 65V                         | 2.0      | \/ppo : 0 0* | .,   |

| VIH     | High-level Input Voltage                        | VDDQ = 2.375~2.62                                           | 25V                         | 1.7      | VDDQ+0.3*    | V    |

| \ /··   | Law law law at Nations                          | VDDQ = 3.135~3.46                                           | 65V                         | 0.2*     | 0.8          | .,   |

| VIL     | Low-level Input Voltage                         | VDDQ = 2.375~2.62                                           | 25V                         | -0.3*    | 0.7          | V    |

| Vон     | High-level Output Voltage                       | Iон = -2.0mA                                                |                             | VDDQ-0.4 |              | V    |

| Vol     | Low-level Output Voltage                        | IOL = 2.0mA                                                 |                             |          | 0.4          | V    |

|         | Input Current except ZZ and LBO#                | VI = 0V ~ VDDQ                                              | VI = 0V ~ VDDQ              |          | 10           |      |

| ILI     | Input Current of LBO#                           | VI = 0V ~ VDDQ                                              |                             |          | 100          | μA   |

|         | Input Current of ZZ                             | VI = 0V ~ VDDQ                                              |                             |          | 100          |      |

| ILO     | Off-state Output Current                        | VI (G#) ≥ VIH, VO =                                         | : 0V ~ VDDQ                 |          | 10           | μA   |

|         |                                                 | Device selected;                                            | 4.0ns cycle(250MHz)         |          | 550          |      |

| ICC1    | Power Supply Current : Operating                | Output Open<br>Vi≤Vi⊾ or Vi≥Viн                             | ' I / /nc ovolo/2261/147\ I |          | 500          | mA   |

|         |                                                 | ZZ\(\text{VIL}\)                                            | 5.0ns cycle(200MHz)         |          | 440          |      |

|         |                                                 | Device                                                      | 4.0ns cycle(250MHz)         |          | 220          |      |

| ICC2    | Power Supply Current : Deselected               | deselected<br>VI≤VIL or VI≥VIH                              | 4.4ns cycle(225MHz)         |          | 200          | mA   |

|         |                                                 | ZZ≤VIL                                                      | 5.0ns cycle(200MHz)         |          | 180          | 1117 |

| ICC3    | CMOS Standby Current (CLK stopped standby mode) | Device deselected<br>VI≤Vss+0.2V or VII<br>CLK frequency=0F | ≥VDDQ-0.2V                  |          | 30           | mA   |

| ICC4    | Snooze Mode Standby Current                     | Snooze mode<br>ZZ≥VDDQ-0.2V, LB                             | O#≥Vdd-0.2V                 |          | 30           | mA   |

|         |                                                 | Device selected;<br>Output Open                             | 4.0ns cycle(250MHz)         |          | 160          |      |

| ICC5    | Stall Current                                   | CKE#≥ViH                                                    | 4.4ns cycle(225MHz)         |          | 150          | mA   |

|         |                                                 | Vi≤Vss+0.2V or<br>Vi≥VDDQ-0.2V                              | 5.0ns cycle(200MHz)         |          | 140          |      |

Note17.\*V<sub>ILmin</sub> is −1.0V and V<sub>IH max</sub> is V<sub>DDQ</sub>+1.0V in case of AC(Pulse width≤2ns).

Note18."Device Deselected" means device is in power-down mode as defined in the truth table.

### **CAPACITANCE**

| Symbol   | Parameter                      | Conditions                 |     | Unit |     |       |

|----------|--------------------------------|----------------------------|-----|------|-----|-------|

| Syllibol | Farameter                      | Conditions                 | Min | Тур  | Max | Oilit |

| Cı       | Input Capacitance              | Vi=GND, Vi=25mVrms, f=1MHz |     |      | 6   | pF    |

| Co       | Input / Output(DQ) Capacitance | Vo=GND, Vo=25mVrms, f=1MHz |     |      | 8   | pF    |

Note19. This parameter is sampled.

### THERMAL RESISTANCE

#### 4-Layer PC board mounted (70x70x1.6mmT)

| Cumbal | Parameter                           | Conditions            |     | Unit  |     |      |

|--------|-------------------------------------|-----------------------|-----|-------|-----|------|

| Symbol | Parameter                           | Conditions            | Min | Тур   | Max | Unit |

| θЈА    | Thermal Resistance Junction Ambient | Air velocity=0m/sec   |     | 28.18 |     | °C/W |

|        |                                     | Air velocity=0.5m/sec |     | 24.37 |     | °C/W |

|        |                                     | Air velocity=1m/sec   |     | 22.48 |     | °C/W |

|        |                                     | Air velocity=2m/sec   |     | 20.33 |     | °C/W |

|        |                                     | Air velocity=5m/sec   |     | 17.84 |     | °C/W |

| θЈС    | Thermal Resistance Junction to Case |                       |     | 6.64  |     | °C/W |

Note20. This parameter is sampled.

Systems must be designed to keep Tj below 105 degree C.

Tj: SRAM Junction temperature  $Tj(^{\circ}C)=Ta(^{\circ}C) + \theta JA(^{\circ}C/W) \times Pd(W)$

### AC ELECTRICAL CHARACTERISTICS (Ta=0~70°C, VDD=3.135~3.465V, unless otherwise noted)

### (1)MEASUREMENT CONDITION

Input pulse levels ......VIH=VDDQ, VIL=0V

Input rise and fall times ...... faster than or equal to 1V/ns

Input timing reference levels .......VIH=VIL=0.5\*VDDQ

Output reference levels ......VIH=VIL=0.5\*VDDQ

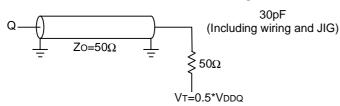

Output load

Fig.1 Output load

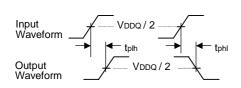

Fig.2 Tdly measurement

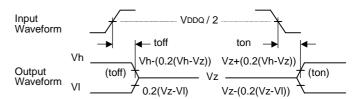

Fig.3 Tri-State measurement

- Note21. Valid Delay Measurement is made from the VDDQ/2 on the input waveform to the VDDQ/2 on the output waveform. Input waveform should have a slew rate of faster than or equal to 1V/ns.

- Note22.Tri-state toff measurement is made from the VDDQ/2 on the input waveform to the output waveform moving 20% from its initial to final Value VDDQ/2.

Note: the initial value is not Vol or Voh as specified in DC ELECTRICAL CHARACTERISTICS table.

Note23. Tri-state ton measurement is made from the VDDQ/2 on the input waveform to the output waveform moving 20% from its initial Value VDDQ/2 to its final Value.

Note: the final value is not Vol or Voh as specified in DC ELECTRICAL CHARACTERISTICS table.

Note24.Clocks,Data,Address and control signals will be tested with a minimum input slew rate of faster than or equal to 1V/ns.

## M5M5V5636GP -25,22,20 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

(2)TIMING CHARACTERISTICS

|             |                                              | Limits |         |     |         |     |         |       |

|-------------|----------------------------------------------|--------|---------|-----|---------|-----|---------|-------|

| Symbol      | Peremeter                                    | 250    | )MHz    | 225 | MHz     | 200 | )MHz    | Unit  |

| Symbol      | Parameter                                    | -25    |         | -   | 22      | -20 |         | Offic |

|             |                                              | Min    | Max     | Min | Max     | Min | Max     |       |

| Clock       |                                              |        |         |     |         |     |         |       |

| tkhkh       | Clock cycle time                             | 4.0    |         | 4.4 |         | 5.0 |         | ns    |

| tkhkl       | Clock HIGH time                              | 1.5    |         | 1.6 |         | 1.8 |         | ns    |

| tklkh       | Clock LOW time                               | 1.5    |         | 1.6 |         | 1.8 |         | ns    |

| Output time | es                                           |        |         |     |         |     |         |       |

| tkhqv       | Clock HIGH to output valid                   |        | 2.6     |     | 2.8     |     | 3.2     | ns    |

| tkhqx       | Clock HIGH to output invalid                 | 1.5    |         | 1.5 |         | 1.5 |         | ns    |

| tKHQX1      | Clock HIGH to output in LOW-Z                | 1.5    |         | 1.5 |         | 1.5 |         | ns    |

| tkhqz       | Clock HIGH to output in High-Z               | 1.5    | 2.6     | 1.5 | 2.8     | 1.5 | 3.2     | ns    |

| tGLQV       | G# to output valid                           |        | 2.6     |     | 2.8     |     | 3.2     | ns    |

| tGLQX1      | G# to output in Low-Z                        | 0.0    |         | 0.0 |         | 0.0 |         | ns    |

| tGHQZ       | G# to output in High-Z                       |        | 2.6     |     | 2.8     |     | 3.2     | ns    |

| Setup Time  | es                                           |        |         |     | •       |     |         |       |

| tavkh       | Address valid to clock HIGH                  | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| tckeVKH     | CKE# valid to clock HIGH                     | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| tadvVKH     | ADV valid to clock HIGH                      | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| twvkh       | Write valid to clock HIGH                    | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| tBVKH       | Byte write valid to clock HIGH (BWa#~BWd#)   | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| tevkh       | Enable valid to clock HIGH (E1#,E2,E3#)      | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| tdvkh       | Data In valid clock HIGH                     | 0.8    |         | 1.0 |         | 1.2 |         | ns    |

| Hold Times  | 6                                            |        |         |     |         |     |         |       |

| tkhax       | Clock HIGH to Address don't care             | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

| tKHckeX     | Clock HIGH to CKE# don't care                | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

| tKHadvX     | Clock HIGH to ADV don't care                 | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

| tkhwx       | Clock HIGH to Write don't care               | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

| +IZLIDV     | Clock HIGH to Byte Write don't care          | 0.5    |         | 0.5 |         | 0.5 |         |       |

| tkhbx       | (BWa#~BWb#)                                  | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

| tkhex       | Clock HIGH to Enable don't care (E1#,E2,E3#) | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

| tkhdx       | Clock HIGH to Data In don't care             | 0.5    |         | 0.5 |         | 0.5 |         | ns    |

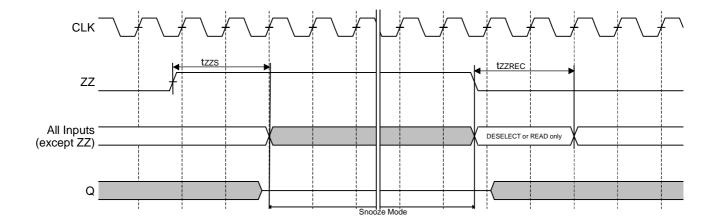

| ZZ          |                                              |        |         |     |         |     |         |       |

| tzzs        | ZZ standby                                   |        | 2*tкнкн |     | 2*tкнкн |     | 2*tкнкн | ns    |

| tzzrec      | ZZ recovery                                  |        | 2*tKHKH |     | 2*tкнкн |     | 2*tKHKH | ns    |

Note25.All parameter except tzzs, tzzrec in this table are measured on condition that ZZ=LOW fix.

Note26. Test conditions is specified with the output loading shown in Fig.1 unless otherwise noted.

Note27. tkHQX1, tkHQZ, tGLQX1, tGHQZ are sampled.

Note28.LBO# is static and must not change during normal operation.

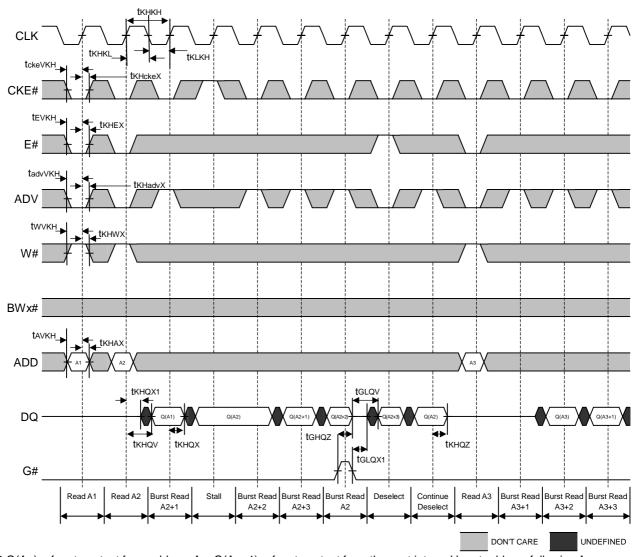

### (3)READ TIMING

Note29.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An. Note30. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW. Note31.ZZ is fixed LOW.

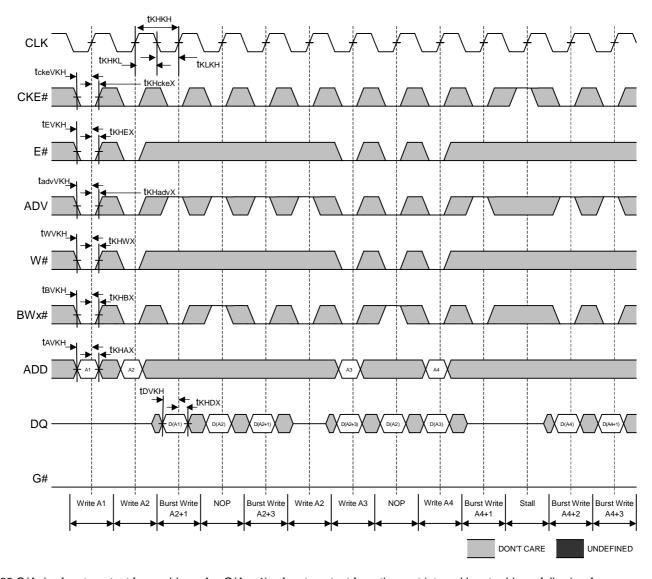

### (4)WRITE TIMING

Note32.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An. Note33. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW. Note34.ZZ is fixed LOW.

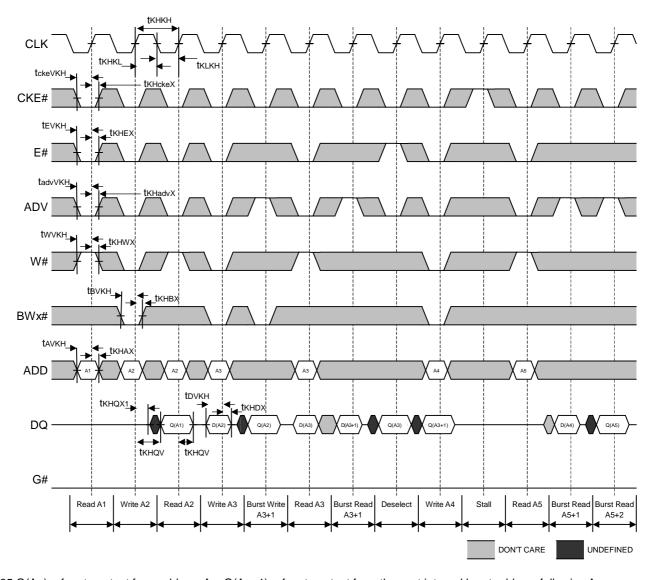

### (5)READ/WRITE TIMING

Note35.Q(An) refers to output from address An. Q(An+1) refers to output from the next internal burst address following An. Note36. E# represents three signals. When E# is LOW, it represents E1# is LOW, E2 is HIGH and E3# is LOW. Note37.ZZ is fixed LOW.

## M5M5V5636GP -25,22,20 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## (6) SNOOZE MODE TIMING

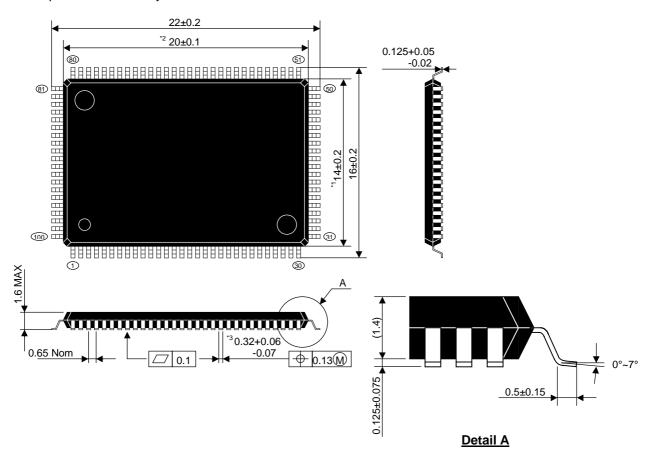

### **PACKAGE OUTLINE**

Plastic 100pin 14x20 mm body

Note38. Dimensions \*1 and \*2 don't include mold flash. Note39 Dimension \*3 doesn't include trim off set. Note40.All dimensions in millimeters.

## M5M5V5636GP -25,22,20 18874368-BIT(524288-WORD BY 36-BIT) NETWORK SRAM

## **REVISION HISTORY**

| Rev. No. | History        | Date             |             |

|----------|----------------|------------------|-------------|

| 0.0      | First revision | January 31, 2003 | Preliminary |

Keep safety first in your circuit designs!

•Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility

that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due

consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of

non-flammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

•These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the

customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric

Corporation or a third party.

•Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any

product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

•All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at

the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or

other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product

distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for

any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home

page (http://www.mitsubishichips.com).

•When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be

sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric

Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

•Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in

which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor

when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical,

aerospace, nuclear, or undersea repeater use.

•The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

• If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese

government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

• Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the

products contained therein.

RENESAS

17/17